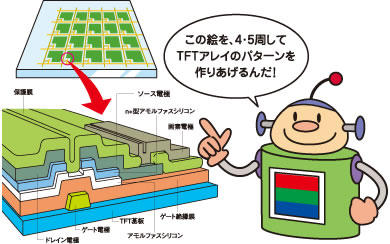

回路設計

画素や周辺回路を、いかに効率よく配置するかなど、回路図を作り検討を重ねます。

フォトマスク作製

フォトマスクは、TFTやCFのパターンをガラス基板に焼付けするための写真のネガに相当します。

基板洗浄

ガラス基板上にゴミ(パーティクル)や汚染(有機物などによる汚れ)があると工程で不良の大きな発生原因になります。洗浄では、ブラシや薬品を使ってこれらを除去することを目的に行われる工程です。

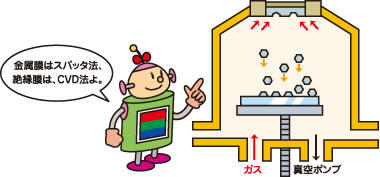

成膜

TFTを形成するために透明電極膜・ゲート電極膜・配線膜をスパッタリングで、アモルファスSi膜・絶縁膜をプラズマCVDで成膜を行ないます。

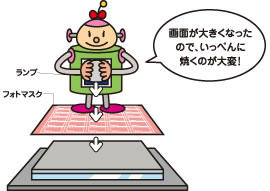

レジスト塗布

感光性材料であるフォトレジストを基板上に極めて薄く均一に塗布を行います。スピン塗布方式やスリット塗布方式などがあります。

露光

基板上のフォトレジストに対して、回路パターン形状をフォトマスク等を介して投影露光するなどして感光させます。

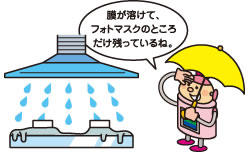

現像

露光された基板を現像することにより、基板上にレジスト像の回路パターン等を形成します。

パターン検査

アレイ基板上に形成されたパターンにオープン、ショート、異物などの欠陥がないか検査します。

ウェットエッチング

膜の露出している部分(レジストで覆われてないところ)をエッチングで除去します。

ドライエッチング

レジスト剥離

その後、不要なレジストも取り除きます。

アニール

薄膜に熱処理を加え基板上の素子の性能を向上させます。